一、实验目的

1、掌握数据流级建模方式的Verilog HDL语言的编程方法;

2、掌握各种操作符的应用;

3、应用数据流级建模方式设计主从D触发器。

二、实验内容

1、掌握数据流级建模方式的Verilog HDL语言的编程方法;

2、基于Verilog HDL利用数据流级建模方式实现主从D触发器。

三、实验原理

1.定义:

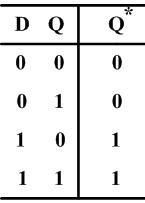

凡在时钟信号作用下,具有如右所示的功能表的

触发器称为D触发器

2.特性方程:

由特性表可写出触发器输出端的方程为:

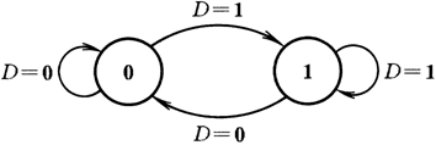

3.状态转换图:

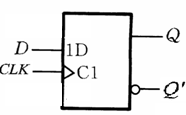

4.逻辑符号:

其逻辑符号如右图所示,为边沿触发器,时钟上升沿触发。

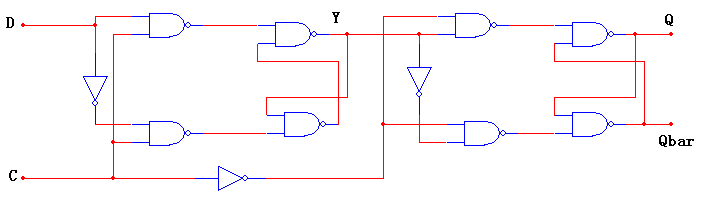

5.主从D触发器结构图:

四、实验设备与器件

安装QuartusII软件的PC机

五、实验步骤

1、设计编写功能模块

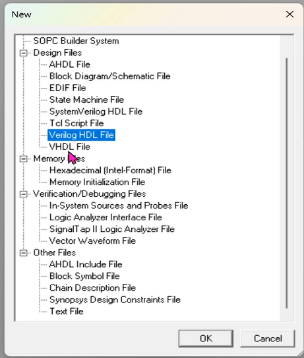

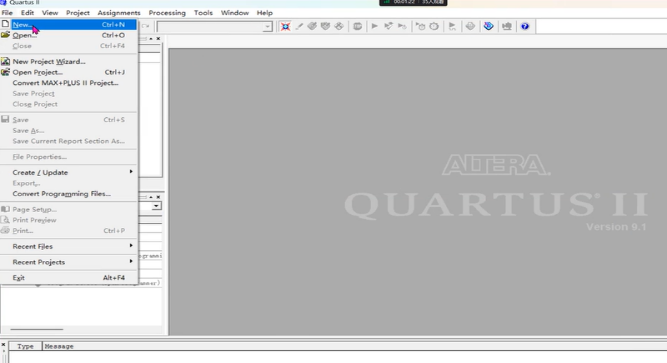

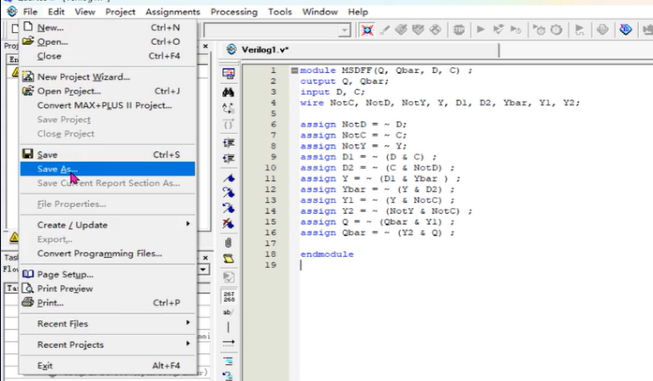

File→New →Verilog HDL file→输入编写好的程序→另存为→选择存储路径(注意路径不要含有中文)

图1 File→New →Verilog HDL file建立新程序编写文件

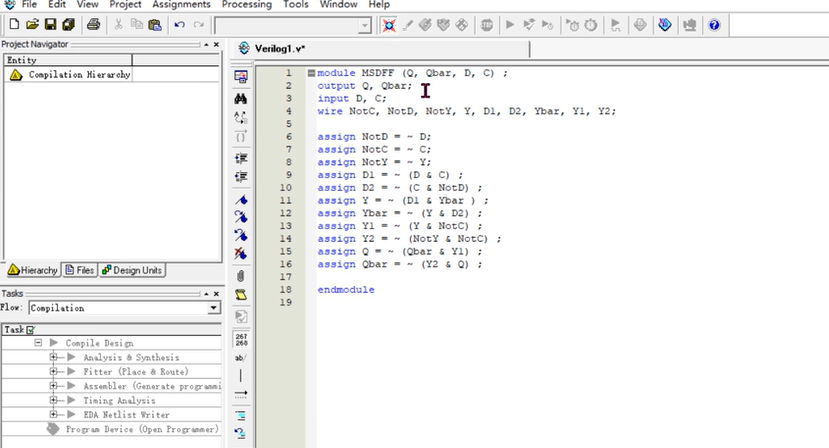

图2 输入编写好的程序

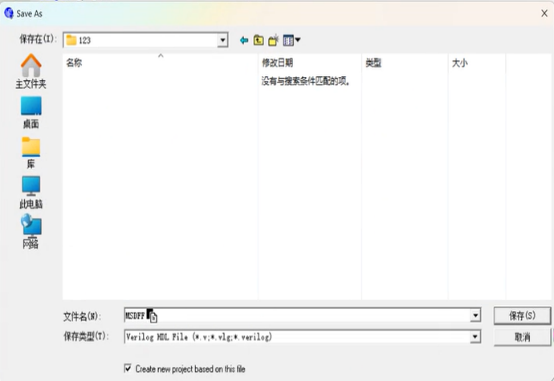

图3 另存为→选择存储路径(注意路径不要含有中文,文件名一定要与模块名一致)

参考程序:

module MSDFF (Q, Qbar, D, C) ;

output Q, Qbar;

input D, C;

wire NotC, NotD, NotY, Y, D1, D2, Ybar, Y1, Y2;

assign NotD = ~ D;

assign NotC = ~ C;

assign NotY = ~ Y;

assign D1 = ~ (D & C) ;

assign D2 = ~ (C & NotD) ;

assign Y = ~ (D1 & Ybar ) ;

assign Ybar = ~ (Y & D2) ;

assign Y1 = ~ (Y & NotC) ;

assign Y2 = ~ (NotY & NotC) ;

assign Q = ~ (Qbar & Y1) ;

assign Qbar = ~ (Y2 & Q) ;

endmodule

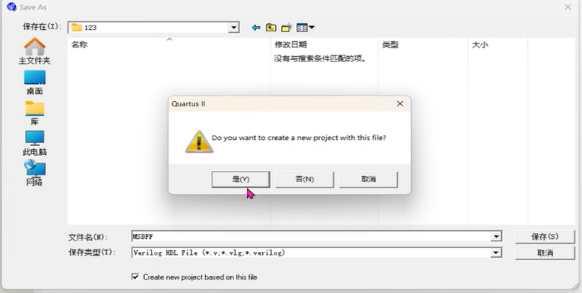

2、建工程文件

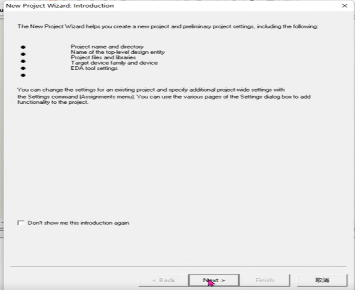

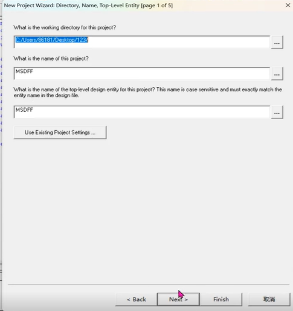

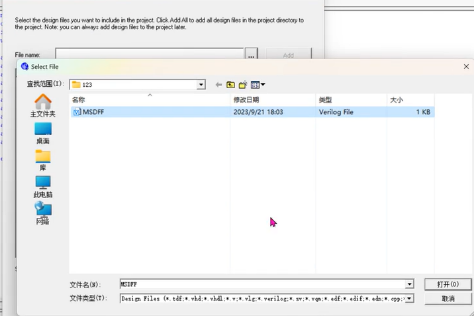

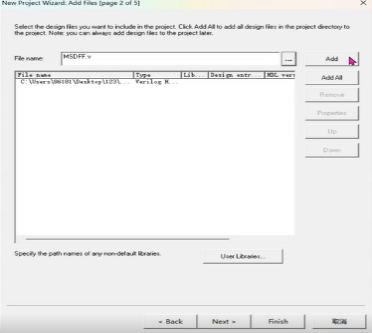

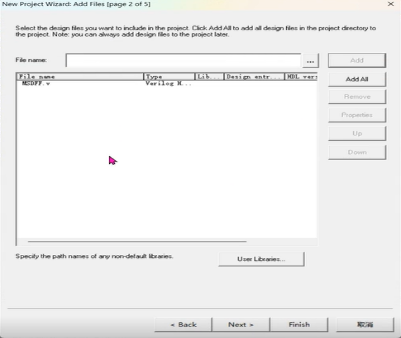

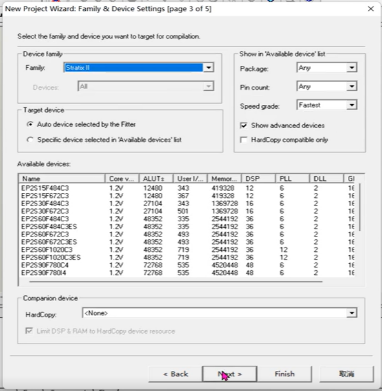

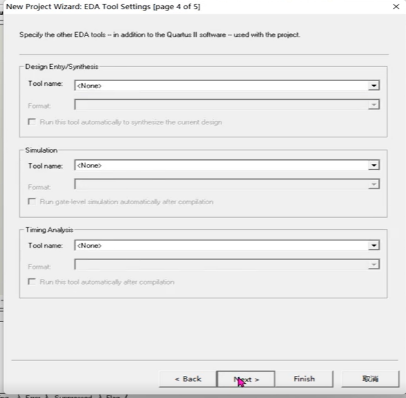

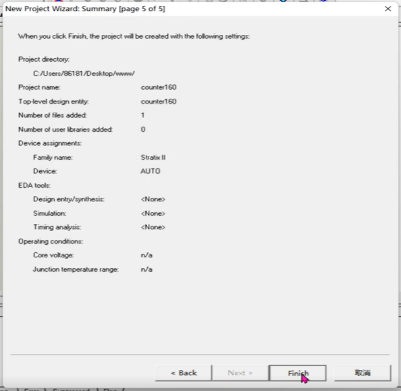

保存后弹出对话框”Do you want to create a new project with this file” →点击“是”→Next→设置路径、项目及顶层模块名称→Next→在弹出的对话框中单击File栏后的按钮,将编写好的Verilog程序加入此工程→Next→选择目标芯片(例:CycloneⅢ系列→Ep3C55F4884C8)→Next→EDA工具设置窗口→Next→finish

图4 建立本设计项目工程文件→next项目工程信息→next

图5 设置路径、项目及顶层模块名称→Next 图6 单击File栏后的…按钮,添加Verilog程序→Next

图7 点击add按键将add.v文件添加入下面对话框中→Next

图8 选择目标芯片→Next→EDA工具设置窗口→Next→finish

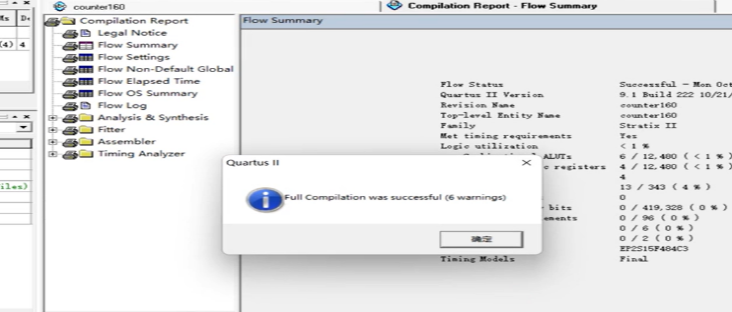

3、编译验证(验证程序编写是否有错误)

图9 点击编译按键进行编译

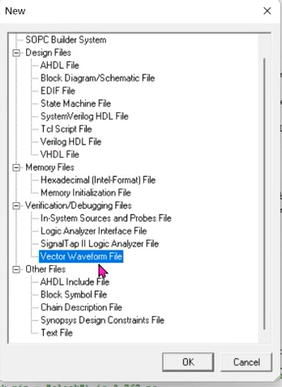

4、功能仿真File→New →vector waveform file→保存

图10 点击File→New →vector waveform file→保存,建立波形仿真文件

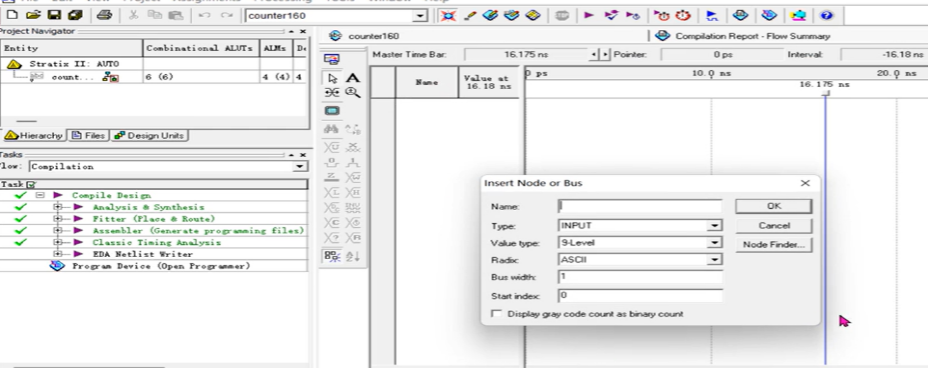

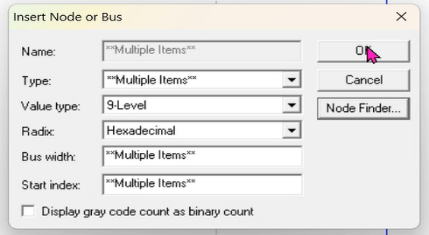

图11 双击Name下方空白处弹出Insert Node or Bus对话框,点击Node Finder…

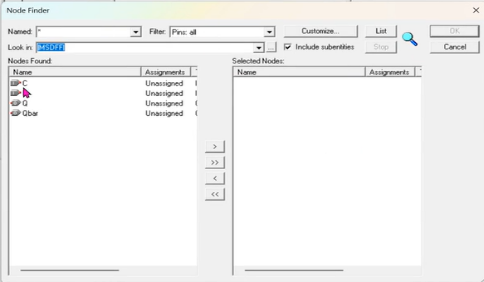

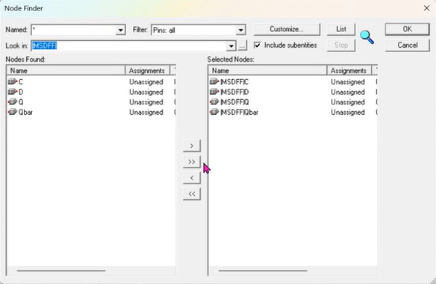

图12 点击List加载模块输入输出引脚→OK

图13 点击OK→添加输入信号信息

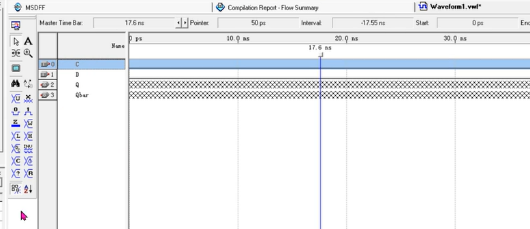

5、添加输入信号信息

图14 点击左侧工具栏添加输入信号信息

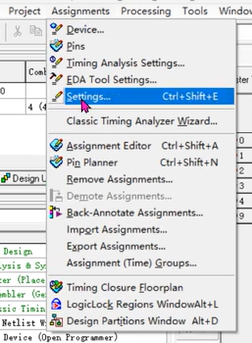

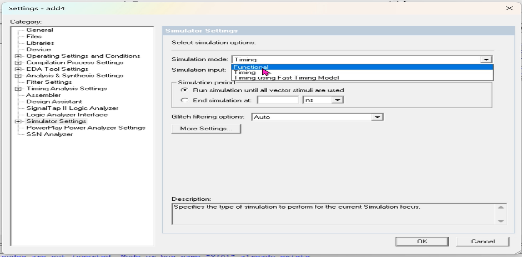

图15 点击Assignments→Settings…→将Timing改成Functional

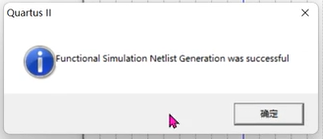

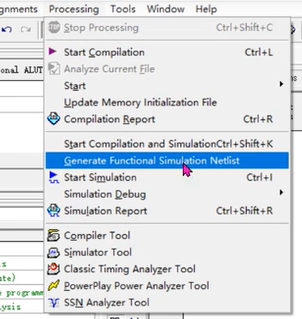

图15 点击Processing→Generate Functional Simulation Netlist→网表文件生成成功

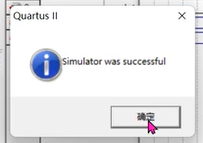

图16 点击波形仿真按钮进行仿真

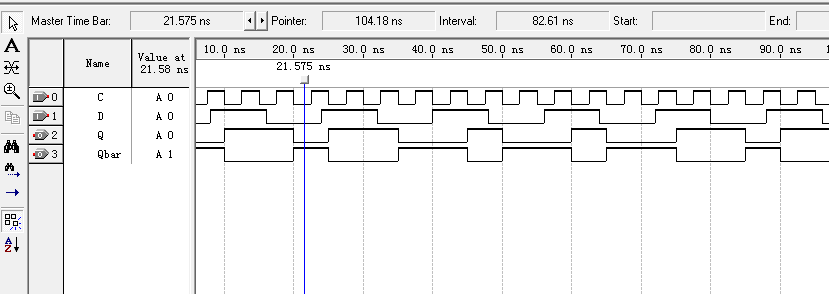

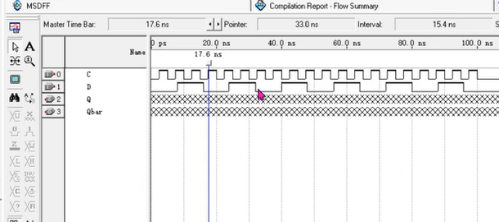

6、产生功能波形(参考波形如下)