组合逻辑电路设计与测试

一、实验目的

1.掌握组合逻辑电路的分析与设计方法。

2.加深对基本门电路使用的理解

二、实验内容

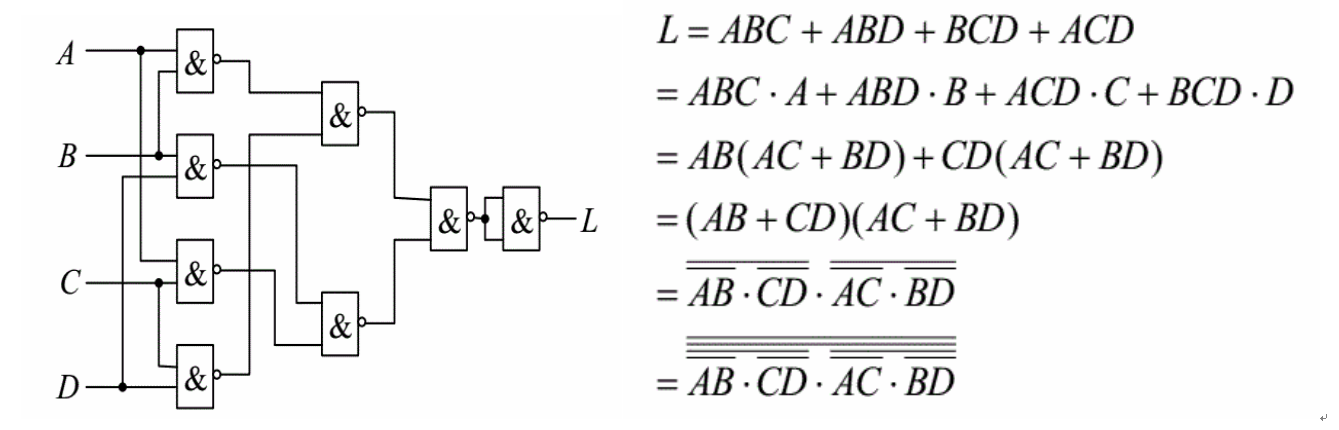

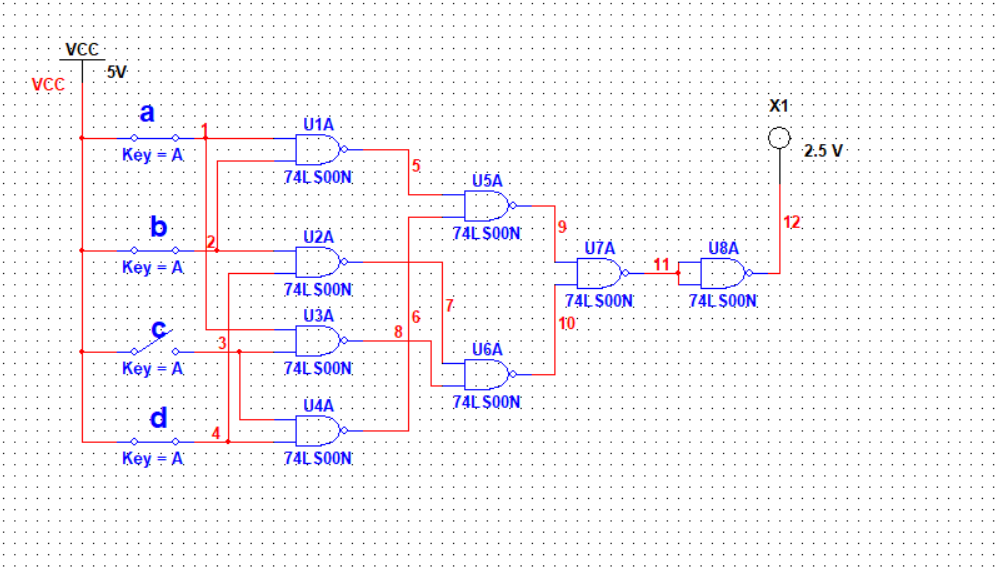

1.设计一个四人无弃权表决电路(多数赞成则提议通过),要求用四2输入与非门来实现。测试并记录功能。

图1

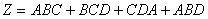

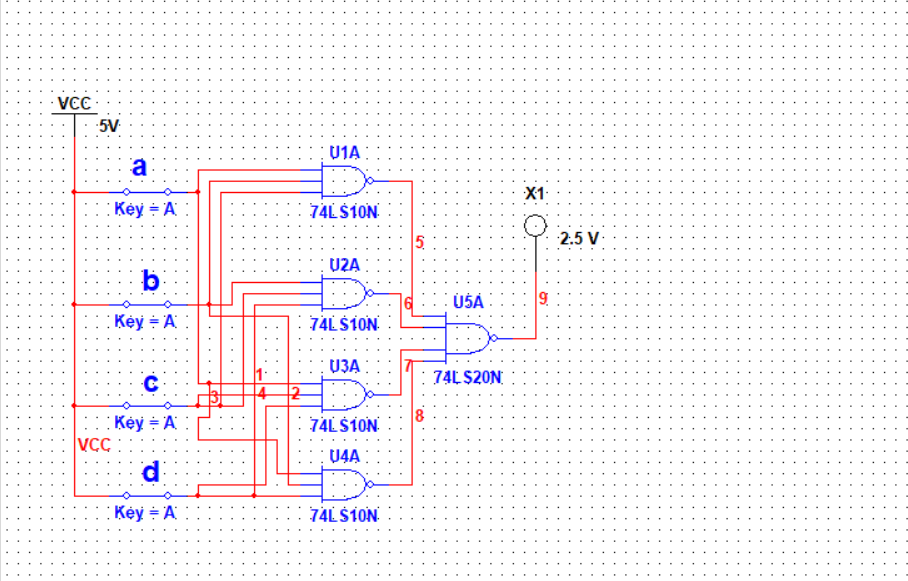

2.设计一个四人无弃权表决电路(多数赞成则提议通过),要求用3输入与非门和4输入与非门来实现,测试并记录功能表。

(1) 用“与非门”设计一个表决电路。当四个输入端中有三个或四个“1”时,输出端才为“1”。

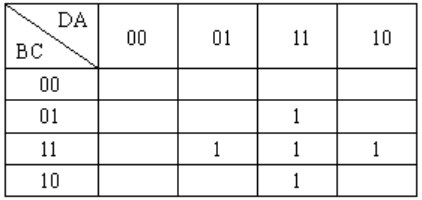

设计步骤:根据题意,列出真值表如表3-1所示,再添入卡诺图表中。

表3-1 表决电路的真值表

D |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

A |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

B |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

C |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

Z |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

图2

然后,由卡诺图得出逻辑表达式,并演化成“与非”的形式:

最后,画出用“与非门”构成的逻辑电路如图所示:

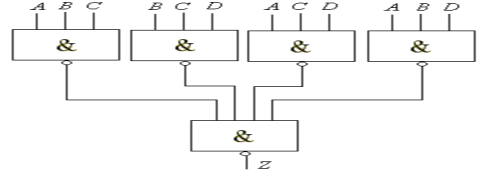

图3

图4

输入端接至逻辑开关(拨位开关)输出插口,输出端接逻辑电平显示端口,自拟真值表,逐次改变输入变量,测试并记录其逻辑功能。

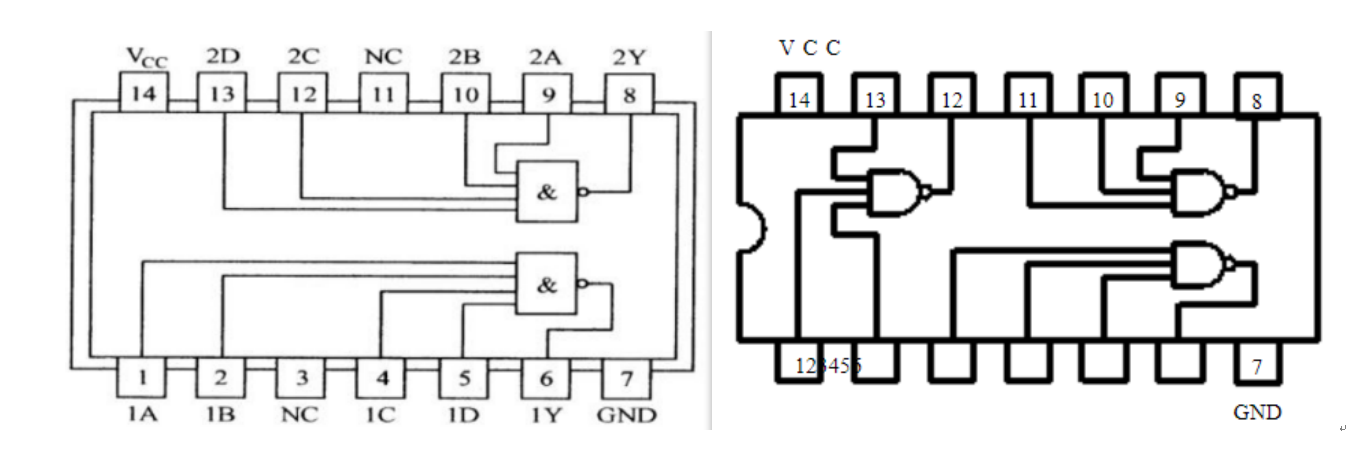

1.三输入与非门

图5

2、四人无弃权表决电路

图6

三、实验原理及说明

1.组合电路是最常用的逻辑电路,可以用一些常用的门电路来组合完成具有其他功能的门电路。

2.分析组合逻辑电路的一般步骤是:

(1)由逻辑图写出各输出端的逻辑表达式;

(2)化简和变换各逻辑表达式;

(3)列出真值表;

(4)根据真值表和逻辑表达式对逻辑电路进行分析,最后确定其功能。

3.设计组合逻辑电路的一般步骤与上面相反,是:

(1)根据任务的要求,列出真值表;

(2)用卡诺图或代数化简法求出最简的逻辑表达式;

(3)根据表达式,画出逻辑电路图,用标准器件构成电路;

(4)最后,用实验来验证设计的正确性。

四、实验设备

一台安装Multisim的PC机。