加法器与数值比较器

一、实验目的

1、掌握半加器和全加器的工作原理。

2、掌握数值比较器的工作原理。

3、掌握四位数值比较器74LS85的逻辑功能。

二、实验内容

1、设计一个半加器:将数字逻辑电路实验箱扩展板插在实验箱相应位置,并固定好,插上实验需要的芯片,用门电路设计组成一个半加器,连线并验证其逻辑功能,自拟真值表,并将实验结果填入表中。

2、设计一个全加器:用门电路组成一个全加器,连线并验证其逻辑功能,自拟真值表,并将实验结果填入表中与逻辑表达式加以比较。

3、验证74LS85的逻辑功能。

4、用简单的逻辑门电路设计一个二位二进制比较器,画出逻辑电路图,将实验结果填入到自制的表格中。

三、实验原理及说明

1、半加器

半加器是下表逻辑功能的电路, 由表可以看出这种加法运算只考虑了两个加数本身, 而没有考虑由低位来的进位, 所以称为半加。下面就是一个最简单的半加器的真值表:

被加数A |

加数B |

和数S |

进位数C |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

由真值表可得:

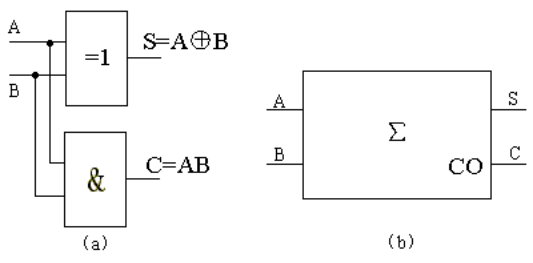

设计电路如下:

设计电路如下:

图1

2、全加器

全加器能进行加数、被加数和低位来的进位信号相加,并根据求和的结果给出该位的进位信号。

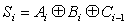

由全加器的真值表可以写出Si和Ci的逻辑表达式:

,

,

Ai |

Bi |

Ci-1 |

Si |

Ci |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

它的原理图为:

图2

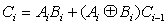

3、数值比较器的原理

在数字系统中, 常常要比较两个数的大小。数值比较器就是对两数A、B进行比较,以判断其大小的逻辑电路。比较结果有A>B、A<B、A=B三种情况。

输入 |

输出 |

A |

B |

FA>B |

FA<B |

FA=B |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

图3

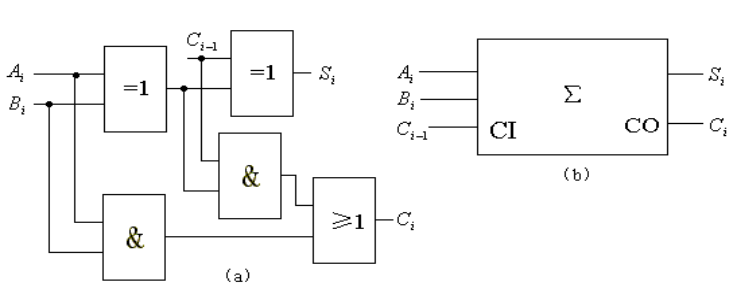

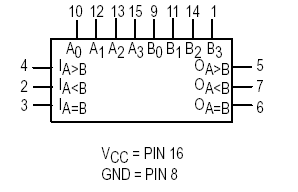

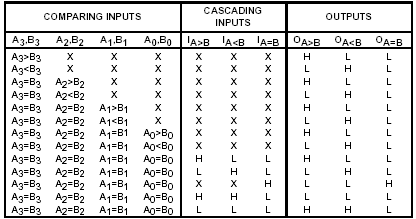

4、 集成数值比较器74LS85

集成数值比较器74LS85是四位数值比较器,它的管脚图和真值表如下:

图4

图5

四、实验设备

一台安装Multisim的PC机。