RISC处理器模型机实验

一、实验目的

1、掌握精简指令系统计算机(RISC)的含义及其工作流程。

2、了解RISC处理器的设计方法。

3、定义若干条机器指令,观察其运行过程和运行结果。

二、实验环境

COP2000软件

三、实验原理及说明

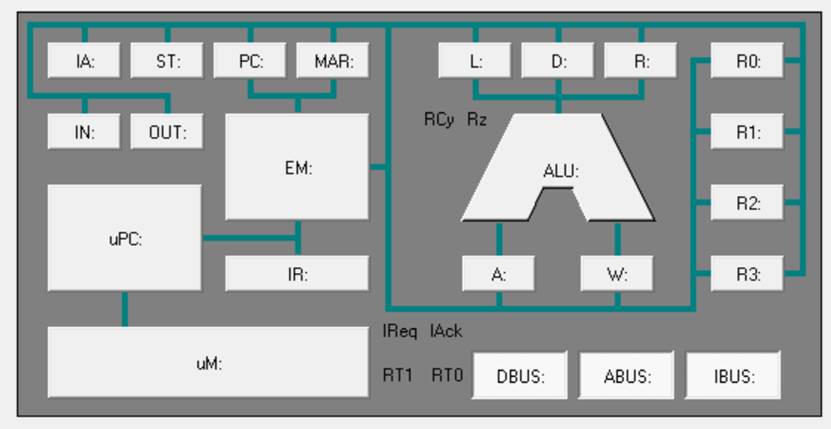

1、COP2000总体结构

COP2000模型机包括了一个标准CPU所具备所有部件,这些部件包括:运算器ALU、累加器 A、工作寄存器 W、左移门L、直通门D、右移门R、寄存器组R0-R3、程序计数器PC、地址寄存器MAR、堆栈寄存器ST、中断向量寄存器IA、输入端口 IN、输出端口寄存器 OUT、程序存储器EM、指令寄存器IR、微程序计数器uPC、微程序存储器uM,以及中断控制电路、跳转控制电路。其中运算器和中断控制电路以及跳转控制电路用 CPLD 来实现,其它电路都是用离散的数字电路组成。微程序控制部分也可以用组合逻辑控制来代替。模型机为 8 位机,数据总线、地址总线都为 8 位,但其工作原理与 16 位机相同。相比而言 8 位机实验减少了烦琐的连线,但其原理却更容易被学生理解、吸收。

模型机的指令码为 8 位,根据指令类型的不同,可以有 0 到 2 个操作数。指令码的最低两位用来选择 R0-R3 寄存器,在微程序控制方式中,用指令码做为微地址来寻址微程序存储器,找到执行该指令的微程序。而在组合逻辑控制方式中,按时序用指令码产生相应的控制位。在本模型机中,一条指令最多分四个状态周期,一个状态周期为一个时钟脉冲,每个状态周期产生不同的控制逻辑,实现模型机的各种功能。模型机有 24 位控制位以控制寄存器的输入、输出,选择运算器的运算功能,存储器的读写。如图1所示。

图1

2、实验原理

RISC处理器设计的一般原则:

(1)只选用使用频度高的指令,减小指令系统,使每一条指令能尽快的执行

(2)减少寻址方式,并让指令具有相同的长度

(3)让大部分指令在一个时钟完成

(4)所有指令只有存(ST)、取(LD)指令可访问内存,其他指令均在寄存器间进行运算

(5)使用组合逻辑实现控制器

源程序。

LD A, #12H

STA R0

LDW R0

ADDW A

STA R1

ST A, 20H

JMP 0

END

下面我们给出一个RISC的指令系统。

助记符 |

机器码1 |

机器码2 |

注释 |

_FATCH_ |

000000xx |

|

实验机占用,不可修改。复位后,所有寄存器清0,首先执行_FATCH_指令取指 |

ADDW A |

000001xx |

|

将寄存器W加入累加器A中 |

ADDCW A |

000010xx |

|

将寄存器W值加入累加器A中,带进位 |

SUBW A |

000011xx |

|

从累加器A中减去寄存器W值 |

SUBCW A |

000100xx |

|

从累加器A中减去寄存器W值,带进位 |

ANDW A |

000101xx |

|

累加器A“与”寄存器W值 |

ORW A |

000110xx |

|

累加器A“或”寄存器W值 |

LDW A |

000111xx |

|

将累加器A的值送到寄存器W中 |

LDW R? |

001000xx |

|

将寄存器R?的值送到寄存器W中 |

LDA R? |

001001xx |

|

将寄存器R?送到累加器A中 |

STA R? |

001010xx |

|

将累加器A的值送到寄存器R?中 |

RR A |

001011xx |

|

累加器A右移 |

RL A |

001100xx |

|

累加器A左移 |

RRC A |

001101xx |

|

累加器A带进位右移 |

RLC A |

001110xx |

|

累加器A带进位左移 |

CPL A |

001111xx |

|

累加器A取反,再存入累加器A中 |

LD A, #II |

010000xx |

II |

将立即数送到累加器A中 |

LD A, MM |

010001xx |

MM |

将存储器中MM中的值送到累加器A中 |

ST A, MM |

010010xx |

MM |

将累加器A的值送到存储器MM地址中 |

JMP MM |

010011xx |

|

跳转到地址MM |

JC MM |

010100xx |

|

若进位标志置1,跳转到地址MM |

JZ MM |

010101xx |

|

若零标志位置1,跳转到地址MM |

四、实验步骤

1、在COP2000软件中,用菜单的[文件|调入指令系统/微程序]功能,打开COP2000下的“RISC.INS”,这就是RISC指令/微指令系统。

2、在COP2000软件中,用菜单的[文件|打开文件]功能,打开COP2000下的“EX7.ASM”。

3、执行“单微指令运行”功能,观察执行每条微指令时,寄存器的输入/输出状态,各控制信号的状态,PC及uPC如何工作,并填写下表。

操作前寄存器数值 |

PC=00 |

指令 |

_FATCH_ |

执行过程 |

实验机占用,不可修改。复位后,所有寄存器清0,首先执行_FATCH_指令取指 |

微指令 |

CBFFFF |

指令 |

无 |

状态 |

T0 |

微地址 |

00 |

操作后寄存器数值 |

PC= 、EM= 、IR= 、μPC= |

指令 |

LD A, #12H |

执行过程 |

|

微指令 |

|

状态 |

|

微地址 |

|

操作后寄存器数值 |

PC= 、EM= 、IR= 、μPC= |

微指令 |

|

状态 |

|

微地址 |

|

操作后寄存器数值 |

PC= 、EM= 、IR= 、μPC= 、A= |

指令 |

STA R0 |

执行过程 |

|

微指令 |

|

状态 |

|

微地址 |

|

操作后寄存器数值 |

PC= 、EM= 、IR= 、μPC= 、L= 、 D= 、R= |

指令 |

LDW R0 |

执行过程 |

|

微指令 |

|

状态 |

|

微地址 |

|

操作后寄存器数值 |

PC= 、EM= 、IR= 、μPC= 、R0= |

指令 |

ADDW A |

执行过程 |

|

微指令 |

|

状态 |

|

微地址 |

|

操作后寄存器数值 |

PC= 、EM= 、IR= 、μPC= 、W= |

指令 |

STA R1 |

执行过程 |

|

微指令 |

|

状态 |

|

微地址 |

|

操作后寄存器数值 |

PC= 、EM= 、IR= 、μPC= 、R0= L= 、D= 、R= 、A= |

指令 |

ST A, 20H |

执行过程 |

|

微指令 |

|

状态 |

|

微地址 |

|

操作后寄存器数值 |

PC= 、EM= 、IR= 、μPC= 、R1= |

微指令 |

|

状态 |

|

微地址 |

|

操作后寄存器数值 |

PC= 、EM= 、IR= 、μPC= 、MAR= |

微指令 |

|

状态 |

|

微地址 |

|

操作后寄存器数值 |

PC= 、EM= 、IR= 、μPC= |

指令 |

JMP 00 |

执行过程 |

|

微指令 |

|

状态 |

|

微地址 |

|

操作后寄存器数值 |

PC= 、EM= 、IR= 、μPC= |

指令 |

_FATCH_ |

执行过程 |

|

微指令 |

|

状态 |

|

微地址 |

|

操作后寄存器数值 |

PC= 、EM= 、IR= 、μPC= |

指令 |

LD A, #12H |

执行过程 |

|

微指令 |

|

状态 |

|

微地址 |

|

操作后寄存器数值 |

PC= 、EM= 、IR= 、μPC= |